# MIC3003

# FOM Management IC with Internal Calibration

# General Description

The MIC3003 is a fiber optic module controller which enables the implementation of sophisticated, hot-pluggable fiber optic transceivers with intelligent laser control and an internally calibrated Digital Diagnostic Monitoring Interface per SFF-8472. It essentially integrates all non-datapath functions of an SFP transceiver into a tiny (4mm x 4mm) MLF® package. It also works well as a microcontroller peripheral in transponders or 10Gbps transceivers.

A highly configurable automatic power control (APC) circuit controls laser bias. Bias and modulation are temperature compensated using dual DACs, an on-chip temperature sensor, and NVRAM look-up tables. A programmable internal feedback resistor provides a wide dynamic range for the APC. Controlled laser turn-on facilitates hot plugging.

An analog-to-digital converter converts the measured temperature, voltage, bias current, transmit power, and received power from analog to digital. An EEPOT provides front-end adjustment of RX power. Each parameter is compared against user-programmed warning and alarm thresholds. Analog comparators and DACs provide fast monitoring of received power and critical laser operating parameters. Data can be reported as either internally calibrated or externally calibrated.

An interrupt output, power-on hour meter, and data-ready bits add user friendliness beyond SFF-8472. The interrupt output and data-ready bits reduce overhead in the host system. The power-on hour meter logs operating hours using an internal real-time clock and stores the result in NVRAM.

In addition to the features listed above which are already implemented in the previous MIC300x controllers, the MIC3003 features an extended temperature range, options to mask alarms and warnings interrupt and TXFAULT, a reset signal source, and the ability to support up to four chips with the same address on the serial interface. It also supports eight-byte SMBus block writes.

Communication with the MIC3003 is via an industry standard 2-wire SMBus serial interface. Nonvolatile memory is provided for serial ID, configuration, and separate OEM and user scratchpad spaces.

Datasheets and support documentation can be found on Micrel's web site at: <a href="www.micrel.com">www.micrel.com</a>.

#### **Features**

- Extended temperature range

- · Alarms and warnings interrupt and TXFAULT masks

- Capability to support up to four MIC3003 on one SMBus

- APC or constant-current laser bias

- Turbo mode for APC loop start-up and shorter laser turn on time

- Supports multiple laser types and bias circuit topologies

- Integrated digital temperature sensor

- Temperature compensation of modulation, bias, bias fault and alarm thresholds via NVRAM look-up tables

- NVRAM to support GBIC/SFP serial ID function

- User writable EEPROM scratchpad

- Reset signal compatible with some new systems requirements

- Diagnostic monitoring interface per SFF-8472

- Monitors and reports critical parameters: temperature, bias current, TX and RX optical power, and supply voltage

- S/W control and monitoring of TXFAULT, RXLOS, RATESELECT, and TXDISABLE

- Internal or external calibration

- EEPOT for adjusting RX power measurement

- · Power-on hour meter

- · Interrupt capability

- Extensive test and calibration features

- 2-wire SMBus-compatible serial interface

- SFP/SFP+ MSA and SFF-8472 compliant

- 3.0V to 3.6V power supply range

- 5V-tolerant I/O

- Available in (4mm x 4mm) 24-pin MLF<sup>®</sup> package

# Applications

- · SFP/SFP+ optical transceivers

- SONET/SDH transceivers and transponders

- · Fibre Channel transceivers

- 10Gbps transceivers

- · Free space optical communications

- · Proprietary optical links

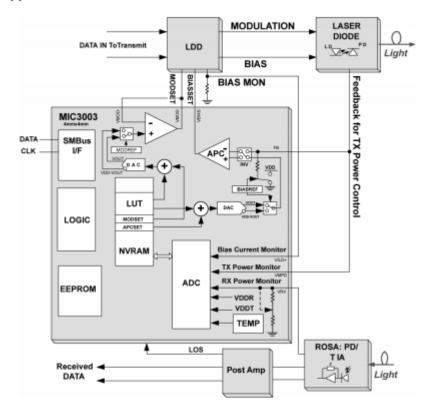

# Typical Application

# Ordering Information

| Part Number                 | Package Type | Junction Temp. Range | Package Marking                         | Lead<br>Finish    |

|-----------------------------|--------------|----------------------|-----------------------------------------|-------------------|

| MIC3003GML                  | 24-pin MLF®  | -45°C to +105°C      | 3003<br>with Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

| MIC3003GMLTR <sup>(1)</sup> | 24-pin MLF®  | -45°C to +105°C      | 3003<br>with Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

#### Note:

Tape and Reel.

# **Pin Configuration**

24-Pin MLF® (MLF-24)

# **Pin Description**

| Pin Number | Pin Name   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB         | Analog Input. Feedback voltage for the APC loop op-amp. Polarity and scale are programmable<br>via the APC configuration bits I OEMCFG1. Connect to V <sub>BAS</sub> if APC is not used.                                                                                                                                                                                                              |

| 2          | VMPD       | Analog Input. Multiplexed A/D converter input for monitoring transmitted optical power via a monitor photodiode. In most applications, VMPD will be connected directly to FB. The input range is 0 - V <sub>REF</sub> or 0 - V <sub>REF</sub> /4 depending upon the setting of the APC configuration bits                                                                                             |

| 3          | GNDA       | Ground return for analog functions.                                                                                                                                                                                                                                                                                                                                                                   |

| 4          | VDDA       | Power supply input for analog functions.                                                                                                                                                                                                                                                                                                                                                              |

| 5          | VILD-      | Analog Input. Reference terminal for the multiplexed pseudo-differential A/D converter inputs for monitoring laser bias current via a sense resistor (VILD+ is the sensing input). Tie to $V_{DD}$ or GND to reference the voltage sensed on VILD+ to $V_{DD}$ or GND, respectively.                                                                                                                  |

| 6          | VILD+      | Analog Input. Multiplexed A/D input for monitoring laser bias current via a sense resistor (signal input); accommodates inputs referenced to V <sub>DD</sub> or GND (see pin 5 description).                                                                                                                                                                                                          |

| 7          | SHDN/TXFIN | Digital output/Input; programmable polarity. When used as shutdown output (SHDN), OEMCFG3 bit 2 set to 0, SHDN is asserted at the detection of a fault condition if OEMCFG4 bit 7 is set to 0. If OEMCFG4 bit 7 is set to 1, a fault condition will not assert SHDN. When programmed as TXFIN, it is an input for external fault signals to be ORed with the internal fault sources to drive TXFAULT. |

| 8          | VRX        | Analog Input. Multiplexed A/D converter input for monitoring received optical power. The input range is 0 to V <sub>REF</sub> . A 5-bit programmable EEPOT on this pin provides coarse calibration and ranging of the RX power measurement.                                                                                                                                                           |

| 9          | RS1        | Digital Input; Transmitter Rate Select Input; ORed with soft rate select bit SRS1 to determine the<br>state of the TRSOUT pin. The state of this pin is always reflected in the RS1S bit.                                                                                                                                                                                                             |

| 10         | TXFAULT    | Digital Output; Open-Drain, with programmable polarity. If OEMCFG5 bit 4 is set to 0, a high level indicates a hardware fault impeding transmitter operation. If OEMCFG5 bit 4 is set to 1, a low level indicates a hardware fault impeding transmitter operation. The state of this pin is always reflected in the TXFLT bit.                                                                        |

| Pin Number | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | TXDISABLE | Digital input; Active high. The transmitter is disabled when this input is high or the STXDIS bit is set to 1. The state of this input is always reflected in the TXDIS bit.                                                                                                                                                                                                                                                                                                   |

| 12         | DATA      | Digital I/O, open-drain, bi-directional serial data input/output.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13         | CLK       | Digital input. Serial clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14         | VIN/INT   | If bit 4 (IE) in the USRCTL register is set to 0 (its default value), this pin is configured as an analog input. If IE bit is set to 1, this pin is configured as an open-drain output.                                                                                                                                                                                                                                                                                        |

|            |           | Analog input: Multiplexed A/D input for monitoring supply voltage, with a 0V to 5.5V input range.<br>Open-drain output: outputs the internally generated active-low interrupt signal /INT.                                                                                                                                                                                                                                                                                     |

| 15         | RS0       | Digital input. Receiver Rate Select input. ORed with soft rate select bit SRS0 to determine the state of the RRSOUT pin. The state of this pin is always reflected in the RS0S bit.                                                                                                                                                                                                                                                                                            |

| 16         | GNDD      | Ground return for digital functions.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17         | QGPO      | Open-drain output. Can be selected (via OEMCFG3 bit 7) to be an open-drain GPO or an active-<br>low, open-drain, pulsed reset signal output controlled by the status of bits [0-2] of byte A2h: FFh.                                                                                                                                                                                                                                                                           |

| 18         | VDDD      | Power supply input for digital functions.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19         | RXLOS/    | Digital output. This programmable polarity, open-drain outputs has two purposes:                                                                                                                                                                                                                                                                                                                                                                                               |

|            | TRSOUT    | If OEMCFG6 bit 2 = 0, indicates the loss of the received signal as indicated by a level of received optical power below the programmed RXLOS comparator threshold; may be wire-ORed with external signals. Normal operation is indicated by a low level when OEMCFG6 bit 3 is set to 0 and a high level when OEMCFG6 bit 3 is set to 1. RXLOS is de-asserted when VRX > LOSFLTn. The LOS bit reflects the state of RXLOS whether driven by the MIC3003 or an external circuit. |

|            |           | If OEMCFG6 bit 2 = 1, TRSOUT is selected. This signal represents the transmitter rate select as<br>per the SFF specification. This output is controlled by the SRS1 bit ORed with the RS1 input.                                                                                                                                                                                                                                                                               |

| 20         | RRSOUT/   | Digital Output. Open-Drain or push-pull.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | GPO       | If OEMCFG3 bit 4 is set to 0, RRSOUT is selected. It represents the receiver rate select as per SFF. This output is controlled by the SRS0 bit ORed with RS0 input and is open drain only.                                                                                                                                                                                                                                                                                     |

|            |           | If OEMCFG3 bit 4 is set to 1, GPO is selected. General-purpose, non-volatile output, it is controlled by the GPO configuration bits in OEMCFG3.                                                                                                                                                                                                                                                                                                                                |

| 21         | COMP      | Analog output. Compensation terminal for the APC loop. Connect a capacitor between this pin and GNDA or VDDA with the appropriate value to tune the APC loop time constant to a desirable value.                                                                                                                                                                                                                                                                               |

| 22         | VBIAS     | Analog output. Buffered DAC output capable of sourcing or sinking up to 10mA under control of<br>the APC function to drive an external transistor or the APCSET pin of a laser diode driver for laser<br>diode DC bias. The output and feedback polarity are programmable to accommodate either an<br>NPN or a PNP transistor to drive a common-anode or common-cathode laser diode.                                                                                           |

| 23         | VMOD-     | Analog input. This pin is the inverting terminal of the VMOD buffer op-amp. Connect to VMOD (gain = 1) or a feedback resistor network to set a different gain value.                                                                                                                                                                                                                                                                                                           |

| 24         | VMOD      | Analog Output. Buffered DAC output to set the modulation current on the laser driver IC. Operates with either a $0 - V_{REF}$ or a $(V_{DD} - V_{REF}) - V_{DD}$ output swing so as to generate either a ground-referenced or a $V_{DD}$ referenced programmed voltage. A simple external circuit can be used to generate a programmable current for those drivers that require a current rather than a voltage input.                                                         |

###

Human Body Model 2kV Machine Model 300V

# Operating Ratings<sup>(2)</sup>

| Power Supply Voltage, VDDA/VDDD+3.0V to +3.6             | V |

|----------------------------------------------------------|---|

| Ambient Temperature Range (T <sub>A</sub> )40°C to +105° | С |

| Package Thermal Resistance                               |   |

| MLF <sup>®</sup> (θ <sub>JA</sub> )43°C/                 | Ν |

### Voltage Input, V<sub>IN</sub> (Pin 14 used as an ADC Input)

| Symbol            | Parameter           | Condition                                                                    | Min  | Тур | Max | Units |

|-------------------|---------------------|------------------------------------------------------------------------------|------|-----|-----|-------|

| VIN               | Input Voltage Range | -0.3 V ≤ V <sub>DD</sub> ≤ 3.6V                                              | GNDA |     | 5.5 | V     |

| I <sub>LEAK</sub> | Input Current       | V <sub>IN</sub> = V <sub>DD</sub> or GND; V <sub>AUX</sub> = V <sub>IN</sub> |      | 55  |     | μА    |

| C <sub>IN</sub>   | Input Capacitance   |                                                                              |      | 10  |     | pF    |

### Digital-to-Voltage Converter Characteristics (V<sub>MOD</sub>, V<sub>BIAS</sub>)

| -     | •                                | 1 = 50.                                 |      |     |     |

|-------|----------------------------------|-----------------------------------------|------|-----|-----|

|       | Accuracy                         | -40°C ≤ T <sub>A</sub> ≤ +105°C, Note 7 | ±1   | 2.0 | %fs |

| tconv | Conversion Time                  | Note 8                                  |      | 20  | ms  |

| DNL   | Differential Non-linearity Error | Note 8                                  | ±0.5 | ±1  | LSB |

#### Bias Current Sense Inputs, V<sub>II</sub>n+, V<sub>II</sub>n-

| V <sub>ILD</sub>  | Differential Input Signal Range,<br> V <sub>ILD</sub> + - V <sub>ILD</sub> - |                                                 | 0 |      | V <sub>REF</sub> /4 | mV |

|-------------------|------------------------------------------------------------------------------|-------------------------------------------------|---|------|---------------------|----|

| I <sub>IN+</sub>  | V <sub>ILD</sub> <sup>+</sup> input current                                  |                                                 |   |      | ±1                  | μΑ |

| I <sub>IN</sub> _ | V <sub>ILD</sub> - input current                                             | V <sub>ILD</sub> - referred to V <sub>DDA</sub> |   | +150 |                     | μΑ |

|                   | $ V_{ILD}^+ - V_{ILD}^-  = 0.3V$                                             | V <sub>ILD</sub> <sup>-</sup> referred to GND   |   | -150 |                     | μΑ |

| CIN               | Input Capacitance                                                            |                                                 |   | 10   |                     | pF |

#### APC Op Amp, FB, VBIAS, COMP

| GBW               | Gain Bandwidth Product                                         | C <sub>COMP</sub> = 20pF; Gain = 1                     |                        | 1     |      | MHz   |

|-------------------|----------------------------------------------------------------|--------------------------------------------------------|------------------------|-------|------|-------|

| TC <sub>VOS</sub> | Input Offset Voltage Temperature<br>Coefficient <sup>(4)</sup> |                                                        |                        | 1     |      | μV/°C |

| V <sub>OUT</sub>  | Output Voltage Swing                                           | I <sub>OUT</sub> = 10mA, SRCE bit = 1                  | GNDA                   |       | 1.25 | ٧     |

|                   |                                                                | I <sub>OUT</sub> = -10mA, SRCE bit = 0                 | V <sub>DDA</sub> -1.25 |       | VDDA | ٧     |

| Isc               | Output Short-Circuit Current                                   |                                                        |                        | 55    |      | mA    |

| tsc               | Short Circuit Withstand Time                                   | T <sub>J</sub> ≤ 150°C, Note 8                         |                        |       |      | sec   |

| PSRR              | Power Supply Rejection Ratio                                   | C <sub>COMP</sub> = 20pF; gain = 1, to GND             |                        | 55    |      | dB    |

|                   |                                                                | C <sub>COMP</sub> = 20pF; gain = 1, to V <sub>DD</sub> |                        | 40    |      |       |

| A <sub>MIN</sub>  | Minimum Stable Gain                                            | C <sub>COMP</sub> = 20pF, note 8                       |                        |       | 1    | V/V   |

| ΔV/Δt             | Slew Rate                                                      | C <sub>COMP</sub> = 20pF; gain = 1                     |                        | 3     |      | V/µs  |

| ΔRFB              | Internal Feedback Resistor<br>Tolerance                        |                                                        |                        | ±20   |      | %     |

| ΔRFB/Δt           | Internal Feedback Resistor<br>Temperature Coefficient          |                                                        |                        | 25    |      | ppm/C |

| ISTART            | Laser Start-up Current Magnitude                               | START = 01 <sub>h</sub>                                |                        | 0.375 |      | mA    |

|                   |                                                                | START = 02h                                            |                        | 0.750 |      | mA    |

|                   |                                                                | START = 04h                                            |                        | 1.500 |      | mA    |

|                   |                                                                | START = 08 <sub>h</sub>                                |                        | 3.000 |      | mA    |

| CIN               | Pin Capacitance                                                |                                                        |                        | 10    |      | pF    |

#### lotes:

- 7. Does not include quantization error.

- 8. Guaranteed by design and/or testing of related parameters. Not 100% tested in production.

## Electrical Characteristics

For typical values, T<sub>A</sub> = 25°C, V<sub>DDA</sub> = V<sub>DDD</sub> = +3.3V, unless otherwise noted. **Bold** values are guaranteed for +3.0V ≤ (V<sub>DDA</sub> = V<sub>DDD</sub>) ≤ 3.6V, T<sub>(min)</sub>, ≤ T<sub>A</sub> ≤ T<sub>(min)</sub>, (6)

| Symbol                                   | Parameter                              | Condition                                                                                                                                          | Min   | Тур   | Max   | Units |

|------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Power Su                                 | pply                                   |                                                                                                                                                    |       |       |       |       |

| I <sub>DO</sub>                          | Supply Current                         | CLK = DATA = V <sub>DD0</sub> = V <sub>DDA</sub> ; TXDISABLE<br>low; all DACs at full-scale; all A/D inputs<br>at full-scale; all other pins open. |       | 2.3   | 3.5   | mA    |

|                                          |                                        | CLK = DATA = V <sub>DDD</sub> = V <sub>DDA</sub> ; TXDISABLE<br>high; FLTDAC at full-scale; all A/D inputs<br>at full-scale; all other pins open.  |       | 2.3   | 3.5   | mA    |

| V <sub>POR</sub>                         | Power-on Reset Voltage                 | All registers reset to default values;<br>A/D conversions initiated.                                                                               |       | 2.9   | 2.98  | ٧     |

| V <sub>uvLo</sub>                        | Under-Voltage Lockout Threshold        | Note 5                                                                                                                                             | 2.5   | 2.73  |       | V     |

| V <sub>HYST</sub>                        | Power-on Reset Hysteresis Voltage      |                                                                                                                                                    |       | 170   |       | mV    |

| t <sub>POR</sub>                         | Power-on Reset Time                    | V <sub>DD</sub> > V <sub>POR,</sub> Note 4                                                                                                         |       | 50    |       | μs    |

| V <sub>REF</sub>                         | Reference Voltage                      |                                                                                                                                                    | 1.210 | 1.225 | 1.240 | V     |

| ΔV <sub>REF</sub> /<br>ΔV <sub>DDA</sub> | Voltage Reference Line Regulation      |                                                                                                                                                    |       | 1.7   |       | mV/V  |

| Temperat                                 | ure-to-Digital Converter Characte      | ristics                                                                                                                                            |       |       |       |       |

|                                          | Local Temperature Measurement<br>Error | -40°C ≤ T <sub>A</sub> ≤ +105°C, Note 6                                                                                                            |       | ±1    | ±3    | °C    |

| tconv                                    | Conversion Time                        | Note 4                                                                                                                                             |       |       | 60    | ms    |

| †SAMPLE                                  | Sample Period                          |                                                                                                                                                    |       |       | 100   | ms    |

|                                          |                                        |                                                                                                                                                    |       |       |       |       |

# Voltage-to-Digital Converter Characteristics (V<sub>RX</sub>, V<sub>AUX</sub>, V<sub>BIAS</sub>, V<sub>MPD</sub>, V<sub>ILD</sub>±)

|                 | Voltage Measurement Error | -40°C ≤ T <sub>A</sub> ≤ +105°C, Note 6 | ±1 | ±2.0 | %fs |

|-----------------|---------------------------|-----------------------------------------|----|------|-----|

| tconv           | Conversion Time           | Note 4                                  |    | 10   | ms  |

| <b>t</b> SAMPLE | Sample Period             | Note 4                                  |    | 100  | ms  |

# Notes:

- Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

- 4. Guaranteed by design and/or testing of related parameters. Not 100% tested in production.

- The MIC3003 will attempt to enter its shutdown state when V<sub>ID</sub> falls below V<sub>UAD</sub>. This operation requires time to complete. If the supply voltage falls too rapidly, the operation may not be completed.

- 6. Does not include quantization error.

### **Electrical Characteristics**

| Symbol                    | Parameter                                       | Condition                                              | Min                                | Тур    | Max                   | Units  |

|---------------------------|-------------------------------------------------|--------------------------------------------------------|------------------------------------|--------|-----------------------|--------|

| V <sub>MOD</sub> Buffer   | r Op-Amp, VMOD, V <sub>MOD</sub> -              |                                                        |                                    |        |                       |        |

| GBW                       | Gain Bandwidth                                  | C <sub>COMP</sub> = 20pF; gain = 1                     | T                                  | 1      |                       | MHz    |

| TC <sub>VOS</sub>         | Input Offset Voltage Temperature<br>Coefficient |                                                        |                                    | 1      |                       | μV/°C  |

| IBIAS                     | V <sub>MOD</sub> -Input Current                 |                                                        |                                    | ±0.1   | ±1                    | μΑ     |

| V <sub>OUT</sub>          | Output Voltage Swing                            | I <sub>OUT</sub> = ±1mA                                | GNDA+75                            |        | V <sub>DDA</sub> -75  | mV     |

| I <sub>sc</sub>           | Output Short-Circuit Current                    |                                                        |                                    | 35     |                       | mA     |

| tsc                       | Short Circuit Withstand Time                    | T <sub>J</sub> ≤ 150°C, Note 9                         |                                    |        |                       | sec    |

| PSRR                      | Power Supply Rejection Ratio                    | C <sub>COMP</sub> = 20pF; gain = 1, to GND             |                                    | 65     |                       | dB     |

|                           |                                                 | C <sub>COMP</sub> = 20pF; gain = 1, to V <sub>DD</sub> |                                    | 44     |                       | dB     |

| A <sub>MIN</sub>          | Minimum Stable Gain                             | C <sub>COMP</sub> = 20pF                               |                                    |        | 1                     | V/V    |

| ΔV/ΔΤ                     | Slew Rate                                       | C <sub>COMP</sub> = 20pF; gain = 1                     |                                    | 1      |                       | V/µs   |

| C <sub>IN</sub>           | Pin Capacitance                                 |                                                        |                                    | 10     |                       | pF     |

| Control and               | Status I/O, TXDISABLE, TXFAUL                   | T, RS0, RRSOUT(GPO), SHDN(TXF                          | IN), RXLOS(TR                      | SOUT), | /INT, RS1, 0          | QGPO   |

| V <sub>IL</sub>           | Low Input Voltage                               | i i i i                                                | T                                  |        | 0.8                   | ٧      |

| V <sub>IH</sub>           | High Input Voltage                              |                                                        | 2.0                                |        |                       | V      |

| VoL                       | Low Output Voltage                              | I <sub>OL</sub> ≤ 3mA                                  |                                    |        | 0.3                   | ٧      |

| V <sub>OH</sub>           | High Output Voltage<br>(applies to SHDN only)   | I <sub>OH</sub> ≤ 3mA                                  |                                    |        | V <sub>DDD</sub> -0.3 | ٧      |

| I <sub>LEAK</sub>         | Input Current                                   |                                                        |                                    |        | ±1                    | μА     |

| C <sub>IN</sub>           | Input Capacitance                               |                                                        |                                    | 10     |                       | pF     |

|                           | ptical Power Input, V <sub>MPD</sub>            |                                                        | •                                  |        |                       |        |

| V <sub>IN</sub>           | Input Voltage Range                             | Note 9                                                 | GNDA                               |        | V <sub>DDA</sub>      | ٧      |

| V <sub>RX</sub>           | Input Signal Range                              | BIASREF=0                                              |                                    |        | V <sub>REF</sub>      | ٧      |

|                           |                                                 | BIASREF=1                                              | V <sub>DDA</sub> -V <sub>REF</sub> |        | V <sub>DDA</sub>      | ٧      |

| C <sub>IN</sub>           | Input Capacitance                               | Note 9                                                 |                                    | 10     |                       | pF     |

| I <sub>LEAK</sub>         | Input Current                                   |                                                        |                                    |        | ±1                    | μA     |

| Received C                | ptical Power Input, VRX, RXPC                   | OT .                                                   |                                    |        |                       |        |

|                           | Input Voltage Range                             | Note 9                                                 | GNDA                               |        | V <sub>DDA</sub>      | ٧      |

| V <sub>RX</sub>           | Valid Input Signal Range<br>(ADC Input Range)   |                                                        | 0                                  |        | V <sub>REF</sub>      | ٧      |

| R <sub>RXPOT(32)</sub>    | End-to-End Resistance                           | RXPOT = 1Fh                                            |                                    | 32     |                       | ΚΩ     |

| ΔRXPOT                    | Resistor Tolerance                              |                                                        |                                    | ±20    |                       | %      |

| ΔΡΧΡΟΤ/ΔΤ                 | Resistor Temperature Coefficient                |                                                        |                                    | 25     |                       | ppm/°C |

| $\Delta V_{RX} V_{RXPOT}$ | Divider Ratio Accuracy                          | 00 ≤ RXPOT ≤ 1F <sub>h</sub>                           | -5                                 |        | +5                    | %      |

| I <sub>LEAK</sub>         | Input Current                                   | RXPOT = 0 (disconnected)                               |                                    |        | ±1                    | μA     |

| C <sub>IN</sub>           | Input Capacitance                               | Note 9                                                 |                                    | 10     |                       | pF     |

| I <sub>LEAK</sub>         | Input Current                                   |                                                        | 1                                  |        | ±1                    | μA     |

#### Note:

9. Guaranteed by design and/or testing of related parameters. Not 100% tested in production.

### **Electrical Characteristics**

| Symbol               | Parameter                                                                | Condition                                                                                                        | Min    | Тур | Max   | Units  |

|----------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|-----|-------|--------|

| Control and          | Status I/O Timing, TXFAULT, TXI                                          | DISABLE, RS0, RRSOUT, and RXLOS                                                                                  |        |     |       |        |

| toff                 | TXDISABLE Assert Time                                                    | From input asserted to optical output at 10% of nominal, C <sub>COMP</sub> = 10nF.                               |        |     | 10    | μs     |

| ton                  | TXDISABLE De-assert Time                                                 | From input de-asserted to optical output at 90% of nominal, C <sub>COMP</sub> = 10nF.                            |        |     | 1     | ms     |

| ЧNIТ                 | Initialization Time                                                      | From power on or transmitter enabled to<br>optical output at 90% of nominal and<br>TX_FAULT de-asserted. Note 10 |        |     | 300   | ms     |

| <sup>†</sup> INIT2   | Power-on Initialization Time                                             | From power on to APC loop-enabled.                                                                               |        |     | 200   | ms     |

| <sup>t</sup> FAULT   | TXFAULT Assert Time                                                      | From fault condition to TXFAULT assertion. Note 10                                                               |        |     | 95    | μs     |

| <sup>t</sup> RESET   | Fault Reset Time                                                         | Length of time TXDISABLE must be<br>asserted to reset fault condition.                                           | 10     |     |       | μs     |

| tLOSS_ON             | RXLOS Assert Time                                                        | From loss of signal to RXLOS asserted.                                                                           |        |     | 95    | μs     |

| tLOSS_OFF            | RXLOS De-assert Time                                                     | From signal acquisition to LOS de-asserted.                                                                      |        |     | 100   | μs     |

| <sup>t</sup> DATA    | Analog Parameter Data Ready                                              | From power on to valid analog<br>parameter data available. Note 10                                               |        |     | 400   | ms     |

| <sup>t</sup> PROP_IN | TXFAULT, TXDISABLE, RXLOS,<br>RS0, RS1 Input Propagation Time            | Time from input change to<br>corresponding internal register bit set or<br>cleared. Note 10                      |        |     | 1     | μs     |

| tPROP_OUT            | TXFAULT, TRSOUT, TRRSOUT,<br>/INT, QGPO Output Propagation<br>Time       | From an internal register bit set or<br>cleared to corresponding output change.<br>Note 10                       |        |     | 1     | μs     |

| Fault Comp           | arators                                                                  |                                                                                                                  |        |     |       |        |

| FLTTMR               | Fault Suppression Timer Clock<br>Period                                  | Note 10                                                                                                          | 0.475  | 0.5 | 0.525 | ms     |

|                      | Accuracy                                                                 |                                                                                                                  | -3     |     | +3    | %/fs   |

| <sup>t</sup> REJECT  | Glitch Rejection                                                         | Maximum length pulse that will not<br>cause output to change state. Note 10                                      | 4.5    |     |       | μs     |

| VSAT                 | Saturation Detection Threshold                                           | High level                                                                                                       |        | 95  |       | %VDD   |

|                      |                                                                          | Low level                                                                                                        |        | 5   |       | %VDD/  |

| Power-On H           | lour Meter                                                               |                                                                                                                  |        |     |       |        |

|                      | Timebase Accuracy                                                        | 0°C ≤ T <sub>A</sub> ≤ +70°, Note 10                                                                             | +5     |     | -5    | %      |

|                      |                                                                          | -40°C ≤ T <sub>A</sub> ≤ +105°C                                                                                  | +10    |     | -10   | %      |

|                      | Resolution                                                               | Note 10                                                                                                          |        | 10  |       | hours  |

| Non-Volatile         | e (FLASH) Memory                                                         |                                                                                                                  |        |     |       |        |

| t <sub>WR</sub>      | Write Cycle Time, Note 11                                                | Measured from the SMBus STOP<br>condition of a one-byte to eight-byte<br>write transaction. Note 10              |        |     | 13    | ms     |

|                      | NVRAM Data Retention                                                     |                                                                                                                  | 100    |     |       | years  |

| Endurance            | Maximum permitted number of write<br>cycles to any single NVRAM location |                                                                                                                  | 10,000 |     |       | cycles |

#### Notes

- 10. Guaranteed by design and/or testing of related parameters. Not 100% tested in production.

- 11. The MIC3003 will not respond to serial bus transactions during an EEPROM write cycle. The host will receive a NACK response during tags.

| Addr  | ess(s)  | Field Size |          |                                                                                                                                                 |

|-------|---------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex   | Dec     | (Bytes)    | Name     | Description                                                                                                                                     |

| 00-3F | 0-63    | 64         | BIASLUT1 | First 64 entries of the bias current temperature compensation LUT (Look-<br>up Table) The additional 12 entries are located in A6: 58h – 63h.   |

| 40-7F | 64-127  | 64         | MODLUT1  | First 64 entries of the modulation current temperature compensation<br>LUT. The additional 12 entries are located in A6:.64h – 6Fh.             |

| 80-BF | 128-191 | 64         | IFTLUT1  | First 64 entries of the bias current fault threshold temperature compensation LUT. The additional 12 entries are located in A6: 70h - 78h.      |

| C0-FF | 192-255 | 64         | HATLUT1  | First 64 entries of the bias current high alarm threshold temperature<br>compensation LUT. The additional 12 entries are located in A6: 7C-87h. |

Table 3. MIC3003 Serial Interface Address Map (Temperature Compensation Tables), Device Address = A4n

| Address(s) |       | Field Size |          |                                                                                    |  |

|------------|-------|------------|----------|------------------------------------------------------------------------------------|--|

| Hex        | Dec   | (Bytes)    | Name     | Description                                                                        |  |

| 00         | 0     | 1          | OEMCFG0  | OEM configuration register 0                                                       |  |

| 01         | 1     | 1          | OEMCFG1  | OEM configuration register 1                                                       |  |

| 02         | 2     | 1          | OEMCFG2  | OEM configuration register 2                                                       |  |

| 03         | 3     | 1          | APCSET0  | APC setpoint register 0                                                            |  |

| 04         | 4     | 1          | APCSET1  | APC setpoint register 1                                                            |  |

| 05         | 5     | 1          | APCSET2  | APC setpoint register 2                                                            |  |

| 06         | 6     | 1          | MODSET0  | Modulation setpoint register 0                                                     |  |

| 07         | 7     | 1          | IBFLT    | Bias current fault-comparator threshold. This register is temperature compensated. |  |

| 08         | 8     | 1          | TXPFLT   | TX power fault threshold                                                           |  |

| 09         | 9     | 1          | LOSFLT   | RX LOS fault-comparator threshold                                                  |  |

| 0A         | 10    | 1          | FLTTMR   | Fault comparator timer setting                                                     |  |

| 0B         | 11    | 1          | FLTMSK   | Fault source mask bits                                                             |  |

| 0C-0F      | 12-15 | 4          | OEMPWSET | Password for access to OEM areas                                                   |  |

| 10         | 16    | 1          | OEMCAL0  | OEM calibration register 0                                                         |  |

| 11         | 17    | 1          | OEMCAL1  | OEM calibration register 1                                                         |  |

| 12         | 18    | 1          | LUTINDX  | Look-up table index read-back                                                      |  |

| 13         | 19    | 1          | OEMCFG3  | OEM configuration register 3                                                       |  |

| 14         | 20    | 1          | APCDAC   | Reads back current APC DAC value (setpoint+offset)                                 |  |

| 15         | 21    | 1          | MODDAC   | Reads back current modulation DAC value (setpoint+offset)                          |  |

| 16         | 22    | 1          | OEMREAD  | Reads back OEM calibration data                                                    |  |

| 17         | 23    | 1          | LOSFLTn  | LOS deassert threshold                                                             |  |

| 18         | 24    | 1          | RXPOT    | RXPOT tap selection                                                                |  |

| 19         | 25    | 1          | OEMCFG4  | OEM configuration register 4                                                       |  |

| 1A         | 26    | 1          | OEMCFG5  | OEM configuration register 5                                                       |  |

| 1B         | 27    | 1          | OEMCFG6  | OEM configuration register 6                                                       |  |

| 1C-1D      | 28-29 | 2          | SCRATCH  | Reserved – do not write; reads undefined.                                          |  |

| 1E         | 30    | 1          | MODSET 1 | Modulation setpoint register 1                                                     |  |

# Serial Data I/O Pin, Data

| Symbol          | Parameter          | Condition             | Min | Тур | Max | Units |

|-----------------|--------------------|-----------------------|-----|-----|-----|-------|

| Vol             | Low Output Voltage | I <sub>OL</sub> = 3mA |     |     | 0.4 | V     |

|                 |                    | I <sub>OL</sub> = 6mA |     |     | 0.6 | V     |

| V <sub>L</sub>  | Low Input Voltage  |                       |     |     | 0.8 | V     |

| V <sub>IH</sub> | High Input Voltage |                       | 2.1 |     |     | V     |

| LEAK            | Input Current      |                       |     |     | ±1  | μА    |

| C <sub>IN</sub> | Input Capacitance  | Note 12               |     | 10  |     | pF    |

#### Serial Clock Input, CLK

| V <sub>L</sub>  | Low Input Voltage  | 2.7V ≤ V <sub>DD</sub> ≤ 3.6V |     |    | 0.8 | V  |

|-----------------|--------------------|-------------------------------|-----|----|-----|----|

| V <sub>IH</sub> | High Input Voltage | 2.7V ≤ V <sub>DO</sub> ≤ 3.6V | 2.1 |    |     | V  |

| ILEAK           | Input Current      |                               |     |    | ±1  | μА |

| C <sub>IN</sub> | Input Capacitance  | Note 12                       |     | 10 |     | pF |

# Serial Interface Timing(4)

| t <sub>1</sub> | CLK (clock) Period                 |                                                                                                              | 2.5 |  |     | μs |  |

|----------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|--|-----|----|--|

| t <sub>2</sub> | Data In Setup Time to CLK High     |                                                                                                              | 100 |  |     | ns |  |

| ts             | Data Out Stable After CLK Low      |                                                                                                              | 300 |  |     | ns |  |

| t <sub>4</sub> | Data Low Setup Time to CLK Low     | Start Condition                                                                                              | 100 |  |     | ns |  |

| t <sub>5</sub> | Data High Hold Time After CLK High | Stop Condition                                                                                               | 100 |  |     | ns |  |

| †DATA          | Data Ready Time                    | From power on to completion of one set<br>of ADC conversions; analog data<br>available via serial interface. |     |  | 400 | ms |  |

# **QGPO Reset Pulse Timing**

| . ] | t <sub>1</sub> | QGPO reset pulse low duration                                 | OEMCFG3 bit 7 = 1<br>A2h:255 (FFh) [2-0] switch to 111 | 112.5 | 125  | 137.5 | μs |

|-----|----------------|---------------------------------------------------------------|--------------------------------------------------------|-------|------|-------|----|

|     | t <sub>2</sub> | QGPO reset de-assertion to the<br>clearing of A2:FFh bits 2:0 | OEMCFG3 bit 7 = 1<br>A2h:255 (FFh) [2-0] ≠ 111         | 20.25 | 22.5 | 24.75 | ms |

#### Note:

12. Guaranteed by design and/or testing of related parameters. Not 100% tested in production.

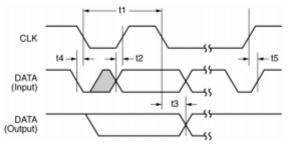

# Serial Interface Timing Diagram

Serial Interface Timing

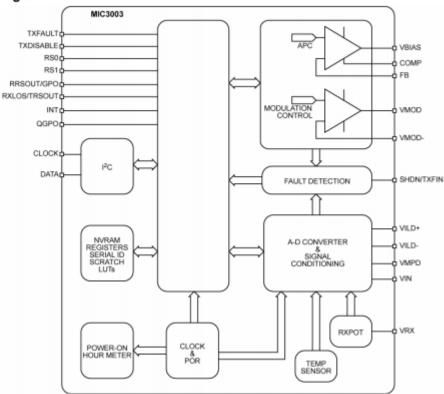

# **Block Diagram**

Figure 1. MIC3003 Block Diagram

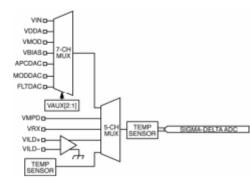

# Analog-to-Digital Converter/Signal Monitoring

A block diagram of the monitoring circuit is shown below. Each of the five analog parameters monitored by the MIC3003 is sampled in sequence. All five parameters are sampled and the results updated within the  $t_{\rm CONV}$  duration given in the "Electrical Characteristics" section. In OEM mode, the channel that is normally used to measure  $V_{\rm IN}$  may be assigned to measure the level of the  $V_{\rm DDA}$  pin or one of five other nodes. This provides a kind of analog loopback for debug and test purposes. The  $V_{\rm AUX}$  bits in OEMCFG0 control which voltage source is being sampled. The various  $V_{\rm AUX}$  channels are level-shifted differently depending on the signal source, resulting in different LSB values and signal ranges. See Table 5.

Figure 2. Analog-to-Digital Converter Block Diagram

# Serial Interface Address Maps

| Address<br>(Decimal) | Field Size<br>(Bytes) | Name                         | Description                                                                   |

|----------------------|-----------------------|------------------------------|-------------------------------------------------------------------------------|

| 0 -95                | 96                    | Serial ID defined by SFP MSA | General-purpose NVRAM; R/W under valid OEM password.                          |

| 96 - 127             | 32                    | Vendor Specific              | Vendor specific EEPROM                                                        |

| 128 – 255            | 128                   | Reserved                     | Reserved for future use. General-purpose NVRAM; R/W under valid OEM password. |

Table 1. MIC3003 Serial Interface Address Map, Device Address = A0<sub>h</sub>

| Address(s) |         | Field Size |                                     |                                                                                                                                                                                                       |

|------------|---------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex        | Dec     | (Bytes)    | Name                                | Description                                                                                                                                                                                           |

| 00-27      | 0-39    | 40         | Alarm and Warning Thresholds        | High/low limits for warnings and alarms; writeable using the OEM password; read-only otherwise.                                                                                                       |

| 28-37      | 40-55   | 16         | Reserved                            | Reserved – do not write; reads undefined.                                                                                                                                                             |

| 38-5B      | 56-91   | 36         | Calibration Constants               | Numerical constants for external calibration; writeable using<br>the OEM password; read-only otherwise.                                                                                               |

| 5C-5E      | 92-94   | 3          | Reserved                            | Reserved – do not write; reads undefined.                                                                                                                                                             |

| 5F         | 95      | 1          | Checksum                            | General-purpose NVRAM; writeable using the OEM password<br>read-only otherwise.                                                                                                                       |

| 60-69      | 96-105  | 10         | Analog Data                         | Real time analog parameter data.                                                                                                                                                                      |

| 6A-6D      | 106-109 | 4          | Reserved                            | Reserved – do not write; reads undefined.                                                                                                                                                             |

| 6E         | 110     | 1          | Control/Status Register             | Control and status bits.                                                                                                                                                                              |

| 6F         | 111     | 1          | Rate Select Control                 | Bits [7-6] control the use of the RS0 and RS1 inputs and the SRS0 and SRS1 register bits.                                                                                                             |

| 70-71      | 112-113 | 2          | Alarm Flags                         | Alarm status bits; read-only.                                                                                                                                                                         |

| 72-73      | 114-115 | 2          | Reserved                            | Reserved – do not write; reads undefined.                                                                                                                                                             |

| 74-75      | 116-117 | 2          | Warning Flags                       | Warning status bits; read-only.                                                                                                                                                                       |

| 76         | 118     | 1          | Extended Control/Status<br>Register | Additional control and status bits.                                                                                                                                                                   |

| 77         | 119     | 1          | Reserved                            | Reserved – do not write; reads undefined.                                                                                                                                                             |

| 78-7E      | 120-126 | 7          | OEMPW                               | OEM password entry field. The four-byte OEM password location can be selected to be 78h-78h (120-123) by setting OEMCFG5 bit 2 to 0 (default) or 78h-7Eh (123-126) by setting OEMCFG5 bit 2 to a one. |

| 7F         | 127     | 1          | Vendor-specific                     | Vendor specific. Reserved - do not write; reads undefined.                                                                                                                                            |

| 80-F7      | 128-247 | 120        | User Scratchpad                     | User-writeable EEPROM. General-purpose NVRAM.                                                                                                                                                         |

| F8-F9      | 248-249 | 2          | Alarms Masks                        | Bit = 0: Corresponding alarm not masked.                                                                                                                                                              |

|            |         |            |                                     | Bit = 1: Corresponding alarm masked.                                                                                                                                                                  |

| FA-FB      | 250-251 | 2          | Warnings Masks                      | Bit = 0: Corresponding warning not masked.                                                                                                                                                            |

|            |         |            |                                     | Bit = 1: Corresponding warning masked.                                                                                                                                                                |

| FC-FD      | 252-253 | 2          | Reserved                            | Reserved – do not write; reads undefined.                                                                                                                                                             |

| FE         | 254     | 1          | USRCTL                              | End-user control and status bits.                                                                                                                                                                     |

| FF         | 255     | 1          | RESETOUT                            | Bits [2:0] of this register control the QGPO reset output (pin 17) If OEMCFG3 bit 7 is set to 1.                                                                                                      |

Table 2. MIC3003 Serial Interface Address Map, Device Address = A2

| Address(s) |         | Field Size |                      |                                                                                                                                                                                                                                                 |

|------------|---------|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEX        | DEC     | (Bytes)    | Name                 | Description                                                                                                                                                                                                                                     |

| 1F         | 31      | 1          | MODSET 2             | Modulation setpoint register 2                                                                                                                                                                                                                  |

| 20-27      | 32-39   | 8          | POHDATA              | Power-on hour meter scratchpad                                                                                                                                                                                                                  |

| 28-47      | 40-71   | 32         | RXLUT                | RX power internal calibration coefficient table. Eight sets of slope and offset coefficients provide a piecewise-linear transfom for the receive power ADC result.                                                                              |

| 48-57      | 72-87   | 16         | CALCOEF              | Slope and offset coefficients used for temperature, voltage, bias current, and transmit power internal calibration                                                                                                                              |

| 58-63      | 88-99   | 12         | IFTLUT2              | Additional 12 entries of the bias current fault threshold temperature<br>compensation LUT.                                                                                                                                                      |

| 64-6F      | 100-111 | 12         | BIASLUT2             | Additional 12 entries of the bias current temperature compensation LUT.                                                                                                                                                                         |

| 70-7B      | 112-123 | 12         | MODLUT2              | Additional 12 entries of the modulation current temperature<br>compensation LUT.                                                                                                                                                                |

| 7C-87      | 124-135 | 12         | HATLUT2              | Additional 12 entries of the bias current high alarm threshold<br>temperature compensation LUT.                                                                                                                                                 |

| 88-CF      | 136-207 | 72         | SCRATCH              | OEM scratchpad area                                                                                                                                                                                                                             |

| D0-DD      | 208-221 | 14         | RXLUTSEG/<br>SCRATCH | Receive power calibration segment delimiters. Each of the eight<br>segments can have its own slope and offset coefficient. Used to refine<br>the shape of the piecewise-linear function used for receive power in<br>internal calibration mode. |

|            |         |            |                      | These bytes may also be part of the OEM scratch pad if the hard coded<br>delimiters option is selected, see the description of OEMCFG6                                                                                                          |

| DE-FA      | 222-250 | 29         | SCRATCH              | OEM scratchpad area                                                                                                                                                                                                                             |

| FB-FC      | 251-252 | 2          | POH                  | Power on hour meter result; read-only                                                                                                                                                                                                           |

| FD         | 253     | 1          | Data Ready Flags     | Data ready bits for each measured parameter; read-only                                                                                                                                                                                          |

| FE         | 254     | 1          | MFG_ID               | Manufacturer identification (Micrel's manufacturer ID is 42, 2Ah)                                                                                                                                                                               |

| FF         | 255     | 1          | DEV_ID               | Device ID and die revision                                                                                                                                                                                                                      |

Table 4. MIC3003 Serial Interface Address Map (OEM Configuration Registers), Device Address = A6h

| Channel | ADC Resolution<br>(bits) | Conditions                                       | Input Range (V)                                           | LSB <sup>(1)</sup> |

|---------|--------------------------|--------------------------------------------------|-----------------------------------------------------------|--------------------|

| TEMP    | 8 or 9                   |                                                  | N/A                                                       | 1°C or 0.5°C       |

| VAUX    | 8                        | See Table 6                                      |                                                           |                    |

| VMPD    | 8                        | GAIN = 0; BIASREF = 0                            | GNDA - VREF                                               | 4.77mV             |

|         |                          | GAIN = 0; BIASREF = 1                            | V <sub>DDA</sub> - (V <sub>DDA</sub> - V <sub>REF</sub> ) |                    |

|         |                          | GAIN = 1; BIASREF = 0 GNDA - V <sub>REF</sub> /4 |                                                           | 1.17mV             |

|         |                          | GAIN = 1; BIASREF = 1                            | VDDA - (VDDA - VREF/4)                                    |                    |

| VILD    | 8                        | VILD- = VDDA                                     | V <sub>DDA</sub> - (V <sub>DDA</sub> - V <sub>REF</sub> ) | 4.77mV             |

|         |                          | VILD- = GNDA                                     | GNDA - V <sub>REF</sub>                                   |                    |

| VRX     | 12                       | RXPOT = 00                                       | 0 - V <sub>REF</sub>                                      | 0.298mV            |

Table 5. A/D Input Signal Ranges and Resolutions

#### Note:

1. Assumes typical VREF value of 1.22V.

| Channel          | VAUX [2:0]            | Input Range (V)        | LSB <sup>(1)</sup> (mV) |

|------------------|-----------------------|------------------------|-------------------------|

| V <sub>IN</sub>  | 000 = 00 <sub>h</sub> | 0.5V to 5.5V           | 25.6mV                  |

| VDDA             | 001 = 01 <sub>h</sub> | 0.5V to 5.5V           | 25.6mV                  |

| VBIAS            | 010 = 02 <sub>h</sub> | 0.5V to 5.5V           | 25.6mV                  |

| V <sub>MOD</sub> | 011 = 03 <sub>h</sub> | 0.5V to 5.5V           | 25.6mV                  |

| APCDAC           | 100 = 04 <sub>h</sub> | OV to V <sub>REF</sub> | 4.77mV                  |

| MODDAC           | 101 = 05 <sub>h</sub> | OV to V <sub>REF</sub> | 4.77mV                  |

| FLTDAC           | 110 = 06 <sub>h</sub> | OV to V <sub>REF</sub> | 4.77mV                  |

Table 6. V<sub>AUX</sub> Input Signal Ranges and Resolutions

#### Note:

Assumes typical V<sub>REF</sub> value of 1.22V.

### Alarms and Warnings Interrupt Source Masking

Alarm and warning violations set the flags in the Alarm and Warning Status Registers, and also assert the interrupt output if they are not masked. If an alarm or

warning is masked, it will not set the interrupt. Table 8 shows the locations of the masking bits. The warning or alarm is masked if the corresponding bit is set to 1.